ANNALS of Faculty Engineering Hunedoara – International Journal of Engineering Tome XIV [2016] – Fascicule 1 [February]

ISSN: 1584-2665 [print; online] ISSN: 1584-2673 [CD-Rom; online] a free-access multidisciplinary publication of the Faculty of Engineering Hunedoara

<sup>1.</sup> Seetaiah KILARU

# DESIGN AND ANALYSIS OF FEASIBLE SYNCHRONOUS RECEIVER ARCHITECTURE

<sup>1.</sup> Department of Electronics & Communication Engineering, Tirumala Engineering College, Andhra Pradesh, INDIA

**ABSTACT**: Wireless communication needs faster speed to give best performance in critical applications. To increase the data rates which is operated under sub millimeter wave range, effective analog synchronous receiver was proposed. This concept neglects the use of feedback loop to the system and follows the feed forward concept. This proposed architecture eliminated many requirements of the conventional technologies like Phase Locked Loop and delay line controller. The proposed deign of Analog Front End have the features of low cost and simple operation. This method also adds the unique feature of phase noise suppression. System level simulations were also presented to check the performance of the feasibility and estimation of performance under several considerations.

Keywords: Phase Locked Loop, Analog Front End, delay line controller, analog synchronous receiver and phase noise suppression

## 1. INTRODUCTION

Technology is increasing in rapid way from time to time. In wireless communication field, the research is going to achieve data rates of the order of Multi-Gbps. Synchronization and carrier acquisitions are the challenging tasks in achieving the required data rates [12]. If we consider the case of mobile users, it is further difficult to provide Multi Gbps data rates because of their moving nature from time to time. In guided communication, to synchronize and to achieve high data rates the designers used same local oscillator at both transmitting and receiving ends [11]. Due to lack of synchronization, we are not implementing Analog Front End (AFE) model in wireless field [2]. Several researches have been done on the implementation of digital base band receivers which are able to handle target transmission. According to the [1], Application Specific Integrated Circuit (ASIC) and customized Analog to Digital converters were used to design the optical transmitter. By following synchronization in digital domain with the help of Quaternary Phase Shift Keying (QPSK), the designer achieved data rates up to 10Gbps. Implementation of Multi Gbps data rates depends on the performance of Digital Signal Processors (DSP'S) and ADC. It possible to obtain this type of high data rates for the system which is operated based on the millimeter wave length bands [1][9].

The proposed architecture completely depends on carrier recovery basis. This is a simple and less complex process and follows feed forwarding technique [12]. To acquire perfect synchronization in terms of gain, phase and frequency, conventional receiver architectures followed Phase Locked Loop (PLL) in their design analysis [13,14]. The proposed architecture is exceptional in this one, it didn't use any PLL. Moreover, the conventional receiver structures used Differential demodulators to extract the exact data. The proposed architecture eliminated this concept also [10].

In this method, the process of demodulation is not depending on factors speed of circuitry and frequency of operation [11,12]. This feature will reduce the cost of the process and also implemented with simple technology rather than existed types of CMOS technologies. Noise is the common phenomenon in communication environment. Suppression of noise is always a

### ANNALS of Faculty Engineering Hunedoara – International Journal of Engineering

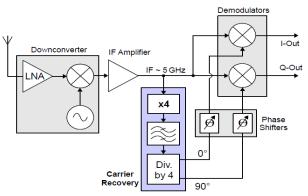

challenging task. This proposed method also provided the feature of phase noise suppression [7]. The following figure shows the architecture of analog receiver.

For the above architecture, we used the range of intermediate frequency as 5GHz. This process uses

the super heterodyne receiver to reduce the complexity of the system. Receiver receives the signal which has the characteristics Quaternary Phase Shift Keying with the frequency 60GHz. As shown in the figure, it first enters into the down converter. Down converter has Low Noise Amplifier (LNA) which amplifies the signal. The output of the down converter was given to the IF amplifier. Depending on the range of intermediate frequency, IF amplifier allows the signal which id required [5]. This output of IF amplifier feeds to the two circuits. One output was fed to the demodulator, which is a critical

Figure 1: Analog receiver architecture

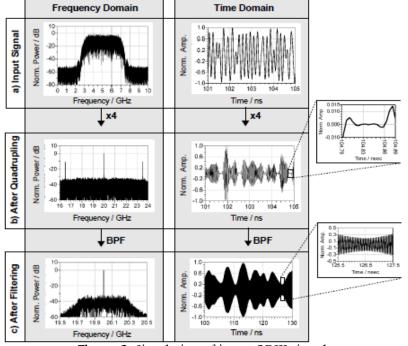

element in this process. The other was given to the carrier recovery. Frequency multiplication was used for carrier recovery [6]. The main advantage behind using the frequency multiplication was to generate the harmonics of carrier signal without the process of modulation. Depending on the order of modulation, it may vary as BPSK, 8PSK or 16PSK. From the figure it was observed that, carrier recovery section doesn't have any feedback loop. Whatever, this section will receiver, it has to forward to the next section, and hence it is called as carry forward or feed forward process [4]. To eliminate the modulated content in carry recovery section, we are quadrupled the QPSK signal. Due to the nature of quadrupling, fourth harmonic of the signal was generated. This output signal passed through the band pass filter and also divided by4 [2]. This introduction of division leads to the generation of new IF range. The selection of divider was depends on the designer choice, here we used static frequency dividers. All this process will take certain time and it may cause delay. The designer has to compensate this time delay for proper function of the system [8]. We used phase shifters to compensate the time delay. The output of the phase shifters was given to the demodulator. At the output, we obtain synchronously demodulated base band symbols [9]. The advantages of the proposed architecture were listed below.

- Less hardware utility: Analog Front End was required to match the input signal range to the manageable base band range. To do this process, we just added quadruple and phase shifters. With this less hard ware utility, we achieved the desired range of output [3].

- Digital base band resolution: digital frequency acquisition was eliminated due to the insertion of alternate carrier recovery domain. Digital base band process is used for the defined scenarios only. This complete digital base band was implemented by using 1 bit.

- Phase noise suppression: unique special feature of this process was phase noise suppression. Noise from both frequency synthesizer and receiver was suppressed effectively.

**3. SIMULATION ANALYSIS** To verify the performance of the system and to check its compatibility with defined conditions, we simulated by using Agilent Advanced Digital System. This simulation is one of the best tools to implement any behavioral model circuits. We introduced defined channel responses to the system

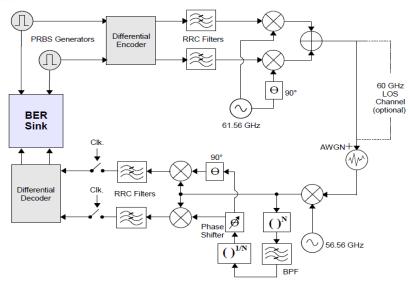

channel responses to the system Figure 2: simulation setup for proposed receiver by using MATLAB interface. The following figure 2 shows the simulation setup.

# ISSN: 1584-2665 [print]; ISSN: 1584-2673 [online]

Two pseudo noise generators were used to generate the transmitted signal with the range of frequency of 60-65GHz. The process of band limitation is mandatory for proper transmission. To do this limitation, we used pulse shaping filters in both transmission and reception. This filter has the roll factor value of 0.34-0.40. The selection of filter is in designer hands, we used Root Raised Cosine (RRC) filters. The modulated signal was generated and it is applied to the receiver using kiosk channel.

The receiver will receives the modulated signal along with the system insertion Additive White Gaussian Noise (AWGN) factor. From the figure 2, it is observable that the selection of PSK was left to user choice. To do simulation, we

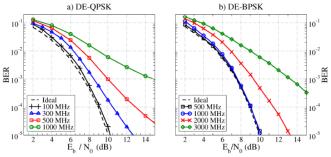

used N value as 2, which represent the BPSK. Differential encoder and decoder were used to resolve all phase mismatch problems. With the help of Monte Carle simulation tool, BER curves were achieved. For 10<sup>6</sup> symbols, simulation process (QPSK) was performed and results were shown in following figure.

Simulated BER for the values of 3 dB bandwidth for band pass filter was shown in following figure. For comparison, differentially encoded QPSK & BPSK at receiver were shown.

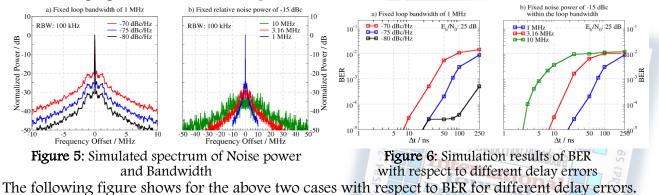

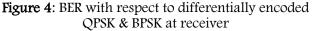

Spectrum of noisy carrier signal was generated under two cases.

1. Bandwidth was constant and noise power will change

2. Noise power was constant and bandwidth will vary.

The following figure shows simulated spectrum of above two cases.

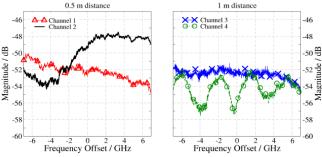

Channel frequency responses were measured under two cases.

Case 1: Perfect aligned antenna (1&3)

Case2: Angular mismatch antennas (2 & 4)

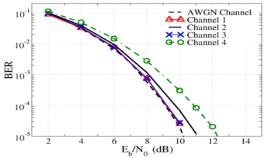

The following figure shows the channel frequency responses with respect to alignment of antennas. The following figure shows the performance of BER for 4 defined channel under the same frequency (60GHz).

Figure 3: Simulation of input QPSK signal

Figure 7: Frequency responses for different channels CONCLUSION

Figure 8: BER for 4 different channel responses

All simulation results proved that the proposed architecture was effective in terms of many factors. By reducing the system rate, we relaxed the bandwidth requirement up to some extent. Phase noise suppression was ultimate feature which was implemented by using the real time frequency synthesizer. It was also shown that, the proposed receiver architecture was not affected from multi path propagation and also proved to operate with the multi Gbps rate.

#### ACKNOWLEDGEMENT

Dr Seetaiah Kilaru was born in Kammavaripalem of Nandigama Mandal, Andhra Pradesh, India on 30th Aug 1988. He finished his Bachelor of Technology from JNTU Hyderabad, India. He pursued his Master of Science in Telecommunication Engineering from Staffordshire University, United Kingdom and Doctorate in Telecommunication Engineering from University of Birmingham. He is working as an Associate Professor in Tirumala Engineering College, Andhra Pradesh, India in Electronics & Communication Engineering. He published more than 25 research papers in various reputed journals. His research areas include wireless and cellular communications, Advanced Signal Processing and Cognitive Radio Network

#### REFERENCES

- [1.] W. Arden, M. Brillouet, P. Cogez, M. Graef, B. Huizing, and R. Mahnkopf. White paper: more-than-Moore [Online]. Available: http://www.itrs.net/papers.html, Accessed: 15.05.2012

- [2.] M. Dubash. Techworld: Moore's law is dead, says Gordon Moore. [Online]. Available: http://news.techworld.com/operating-systems/3477/moores-lawis dead-says-gordon-moore, Accessed: 15.05.2012

- [3.] T. Pfau, S. Ho\_mann, O. Adamczyk, R. Peveling, V. Herath, M. Porrmann, and R. Noe, \Coherent optical communication: Towards realtime systems at 40 Gbit/s and beyond," Optical Express, vol. 16, no. 2, pp. 866-872, 2008

- [4.] S.-J. Huang, Y.-C. Yeh, H. Wang, P.-N. Chen, and J. Lee, \W -Band BPSK and QPSK Transceivers With Costas-Loop Carrier Recovery in 65-nm CMOS Technology," IEEE Journal of Solid-State Circuits, vol. 46, no. 12, pp. 3033 {3046, December 2011.

- [5.] H. Takahashi, T. Kosugi, A. Hirata, K. Murata, and N. Kukutsu, \10-Gbit/s quadrature phase-shift-keying modulator and demodulator for 120-GHz-band wireless links," IEEE Transactions on Microwave Theory and Techniques, vol. 58, no. 12, pp. 4072{4078, December 2010

- [6.] IEEE Std 802.15.3c-2009 (Amendment to IEEE Std 802.15.3-2003)," Institute of Electrical and Electronics Engineers, 2009.

- [7.] IEEE MTT-S. Transactions on terahertz science and technology. [Online]. Available: httpp://www.mtt.org/terahertz.html, Accessed: 15.05.2012.

- [8.] C. Thakkar, L. Kong, K. Jung, A. Frappe, and E. Alon, \A 10 Gb/s 45 mW adaptive 60 GHz baseband in 65 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 47, no. 4, pp. 952{968, April 2012.

- [9.] T. Shima, J. Sato, K. Mizuno, and K. Takinami, \A 60 GHz CMOS PLL synthesizer using a wideband injection-locked frequency divider with fast calibration technique," in Asia-Paci\_c Microwave Conference, 5-8 December 2011, Melbourne, Australia, pp. 1530-1533.

- [10.] G. Liu, A. Trasser, and H. Schumacher, \A 64 to 81 GHz PLL with low phase noise in an 80 GHz SiGe HBT technology," in IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 16-18 January 2012, Santa Clara, CA, pp. 171-174.

- [11.] Kilaru, S., Prasad, Y. A., Kiran, K. S., & Chandra, N. S. (2014). Design and Analysis of Heterogenious Networks. International Journal of Applied Engineering Research, 9(17), 4201-4208.

- [12.] Kilaru, S. (2013, November). Public Safety Communication using Relay Node in LTE-Advanced Technology. In International Journal of Engineering Research and Technology (Vol. 2, No. 11 (November-2013)). ESRSA Publications.

- [13.] Kilaru, S., Harikishore, K., Sravani, T., Anvesh, C. L., & Balaji, T. (2014, August). Review and analysis of promising technologies with respect to Fifth generation networks. In Networks & Soft Computing (ICNSC), 2014 First International Conference on (pp. 248-251). IEEE.

- [14.] Kilaru, S. (2014). Ability of OFDMA in Handling Interference of Femto Cells Under Random Access Process. Journal of Engineering Science and Technology Review, 7(2), 133-136.